Łączenie układów scalonych magistralą I2C - wskazówki aplikacyjne

W jaki sposób wykorzystać I2C do utworzenia sprawnego szeregowego łącza między układami scalonymi - artykuł przedstawia fizyczną implementację magistrali I2C, strukturę protokołu i jej popularne zastosowania.

SMBus a I2C

Wejście szeregowe do ekspandera wejść-wyjść jest przeznaczone dla magistrali SMBus, ale jest również kompatybilne z magistralą I2C. Specyfikacja magistrali SMBus jest oparta na magistrali I2C i została określona przez firmy Intel i Duracell w 1994 roku. Podstawowa różnica polega na tym, że poziomy logiczne w standardowym trybie pracy magistrali I2C zależą do VDD a w przypadku SMBus są stałe. Doświadczenie mówi nam, że w większości przypadków przy VDD o wartości od 3 do 5 woltów nie jest to problem.

Inną różnicą jest to, że SMBus ma zegar ograniczony do 100kHz, podczas gdy I2C ma kilka trybów pracy, obsługujących wyższe częstotliwości taktowania. W kwestii kompatybilności z magistralą ogranicza to maksymalną częstotliwość taktowania do 100kHz lub do standardowego trybu pracy magistrali I2C. Tak więc, z wyjątkiem bardzo szczególnych sytuacji, magistrale SMBus i I2C są kompatybilne.

Komunikacja pomiędzy układami scalonymi i sterowanie nimi za pomocą magistrali równoległych na płytce drukowanej nie jest praktycznym rozwiązaniem. 8-bitowy procesor już wymagałby 16 linii tylko dla danych i wielu innych dla szyny adresowej. Jeszcze bardziej problematyczne jest to, że wiele układów scalonych musi znajdować się na wspólnej magistrali komunikacyjnej. Te wszystkie ścieżki nie mieszczą się na płytce drukowanej. Rozwiązaniem jest połączenie układu scalonego za pomocą szeregowej magistrali komunikacyjnej, takiej jak dwuprzewodowa magistrala Inter-Integrated Circuit (I2C).

W niniejszym artykule opisano pochodzenie magistrali I2C i sposób jej działania w celu utworzenia sprawnego szeregowego łącza między układami scalonymi. Następnie omówiono sposób fizycznej implementacji magistrali I2C, strukturę protokołu i popularne zastosowania tego wszechobecnego rodzaju magistrali komunikacyjnej. Do celów demonstracyjnych wykorzystano przykłady interfejsów I2C i rozwiązania oferowane przez firmę Microchip Technology. W artykule omówione zostaną również podobieństwa i różnice pomiędzy I2C a magistralą typu System Management Bus (SMBus).

Czym jest magistrala I2C?

Magistrala I2C została opracowana przez firmę Phillips Semiconductors, obecnie NXP Semiconductors, na początku lat 80. XX wieku jako prosta dwukierunkowa, dwuprzewodowa magistrala do efektywnej komunikacji i sterowania układami scalonymi na wspólnej płytce drukowanej. Pierwszą specyfikację ukończono w 1992 roku i od tego czasu magistrala ta stała się de facto standardem stosowanym w komponentach ponad 50 producentów układów scalonych. Taka popularność umożliwia systemowe podejście do projektowania, w którym układy scalone mogą być łatwo włączone do struktury magistrali I2C bez konieczności dodatkowego projektowania niestandardowego. Tę samą architekturę współużytkuje kilka innych wyspecjalizowanych magistrali m.in SMBus i Power Management Bus (PMBus).

Magistrala I2C może łączyć wiele układów scalonych i czujników, ponieważ jest magistralą adresowalną - siedmio- lub dziesięciobitowe pole adresowe umożliwia wysyłanie wiadomości do wybranego urządzenia przez urządzenie nadrzędne. Maksymalna prędkość zegara oryginalnej magistrali I2C wynosiła 100 kiloherców (kHz), ale z biegiem lat szybsze tryby pracy przesunęły ten limit do 3,4 megaherców (MHz).

Magistrala I2C wykorzystuje dwa przewody - linię danych (SDA) i linię zegara szeregowego (SCL). SDA i SCL są otwartymi dwukierunkowymi liniami typu otwarty dren / otwarty kolektor i są podłączone do dodatniej szyny zasilającej poprzez źródło prądu lub rezystor podciągający. Do magistrali można podłączyć kilka urządzeń, przy czym maksymalna ich liczba jest ograniczona przez pojemność magistrali. Urządzenie nadrzędne steruje magistralą, a każde urządzenie na magistrali ma swój unikalny adres. Urządzenie nadrzędne może zarówno nadawać, jak i odbierać dane poprzez magistralę (ilustracja 1). I2C obsługuje funkcję multi-master z mechanizmem detekcji kolizji i arbitrażem, aby zapobiegać jednoczesnemu inicjowaniu transferu danych przez więcej niż dwa urządzenia nadrzędne. W tym artykule skoncentrowano się jednak na pojedynczych konfiguracjach urządzenia nadrzędnego.

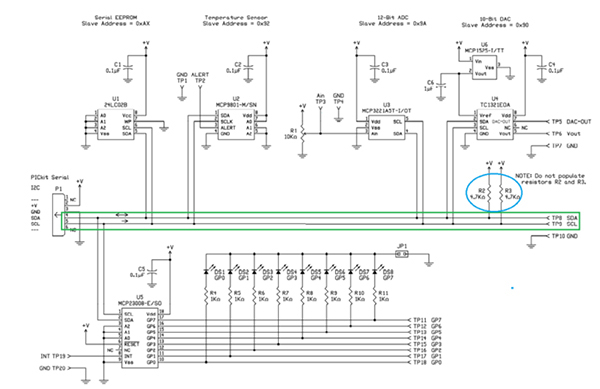

Ilustracja 1: Schemat demonstracyjnej płytki drukowanej firmy Microchip Technology, która umożliwia zastosowanie magistrali I2C i łączy ją z pięcioma różnymi urządzeniami. Urządzenie nadrzędne znajduje się poza płytką i podłączone jest za pomocą złącza P1. Linie SCL i SDA są zaznaczone na zielono, a dwa rezystory podwyższające są zaznaczone na niebiesko. (Źródło ilustracji: Microchip Technology)

Ilustracja 1 przedstawia schemat płytki demonstracyjnej PKSERIAL-I2C1 I2C firmy Microchip Technology. Płytka ta umożliwia implementacje magistrali I2C z zastosowaniem pięciu różnych urządzeń, w tym EEPROM, czujnika temperatury, 12-bitowego przetwornika analogowo-cyfrowego (ADC), 10-bitowego przetwornika cyfrowo-analogowego (DAC) oraz 8-bitowego przetwornika szeregowo-równoległego. Urządzenie nadrzędne nie znajduje się na płytce i jest podłączone za pomocą złącza P1. Linie magistrali SCL i SDA są zaznaczone na zielono, a rezystory podwyższające są zaznaczone na niebiesko.

Poziomy SDA i SCL stanowią na ogół stały procent dodatniego napięcia zasilającego, zwykle oznaczanego jako VDD. Poziomy referencyjne zostały ustalone na poziomie 70% i 30% VDD odpowiednio dla stanu logicznego „1” (stan wysoki) i stanu logicznego „0” (stan niski).

Sygnały zegarowe występują w impulsach z jednym sygnałem na każdy przesyłany bit danych. Dane na linii SDA muszą być poprawne, gdy linia zegara znajduje się w stanie wysokim. Dane można zmieniać tylko, gdy linia zegara znajduje się w stanie niskim.

Z punktu widzenia projektanta, tworzenie nowych projektów jest prostsze, ponieważ interfejsy I2C są zintegrowane z układami scalonymi i nie ma potrzeby osobnego projektowania interfejsu. Każde urządzenie po prostu łączy się bezpośrednio z magistralą. Można dodawać układy scalone do magistrali lub usuwać je bez wpływu na pozostałe obwody (zakładając, że liczba układów scalonych ogółem nie przekracza limitu pojemności). Prosta magistrala dwuprzewodowa minimalizuje ilość wtyków w każdym układzie scalonym oraz ilość przebiegów na płytce drukowanej.