Użycie układów FPGA w projektowaniu systemów czasu rzeczywistego

Aby sprostać wyzwaniom projektowym można wykorzystać układy SoC bezpośrednio programowalnych macierzy bramek (FPGA), tworząc inteligentne, spójne i deterministyczne systemy.

Przykłady układów SoC bezpośrednio programowalnej macierzy bramek (FPGA)

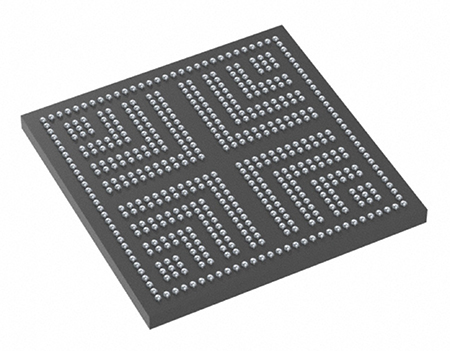

Ilustracja 4: Urządzenie MPFS250T-1FCSG536T2 firmy Microchip do temperatur motoryzacyjnych jest dostępne w obudowie 16 x 16mm z 536 wyprowadzeniami sferycznymi i rastrem 0,5mm. (Źródło ilustracji: Microchip Technology)

Firma Microchip Technology łączy te możliwości i technologie w swoich układach SoC bezpośrednio programowalnych macierzy bramek (FPGA) PolarFire o różnych klasach prędkości, z różnymi parametrami temperaturowymi i różnymi rozmiarami obudów, które pozwalają zaspokoić potrzeby projektantów w szerokiej gamie rozwiązań z liczbą elementów logicznych od 25K do 460K. Dostępne są cztery klasy temperaturowe (wszystkie dla TJ), rozszerzony zakres komercyjny od 0°C do +100°C, zakres przemysłowy od -40°C do +100°C, zakres motoryzacyjny od -40°C do +125°C oraz zakres wojskowy od -55°C do +125°C.

Projektanci mogą dokonywać wyboru spośród urządzeń o standardowej klasie prędkości lub urządzeń o klasie prędkości -1, które są o 15% szybsze. Układy SoC bezpośrednio programowalnych macierzy bramek (FPGA) mogą być zasilane napięciem 1,0V w celu uzyskania najniższej mocy, lub napięciem 1,05V w celu uzyskania wyższych parametrów działania. Są one dostępne w obudowach o różnych rozmiarach, w tym 11 x 11mm, 16 x 16mm i 19 x 19mm.

W przypadku zastosowań wymagających rozszerzonego zakresu temperatur komercyjnych, pracy ze standardową prędkością oraz 254K elementów logicznych w obudowie 19 x 19mm, projektanci mogą sięgnąć po urządzenie MPFS250T-FCVG484EES. W przypadku prostszych rozwiązań wymagających 23K elementów logicznych, projektanci mogą skorzystać z urządzenia MPFS025T-FCVG484E, także z rozszerzonym zakresem temperatur roboczych i standardową prędkością, w obudowie 19 x 19mm. Urządzenie MPFS250T-1FCSG536T2 posiadające 254K elementów logicznych jest przeznaczone do wysokowydajnych systemów motoryzacyjnych i ma zakres temperatur roboczych od -40 do 125°C oraz klasę prędkości -1, co zapewnia o 15% szybszy zegar, w kompaktowej obudowie 16 x 16mm z 536 wyprowadzeniami sferycznymi na rastrze 0,5mm (ilustracja 4).

Platforma rozwojowa układu SoC bezpośrednio programowalnej macierzy bramek (FPGA)

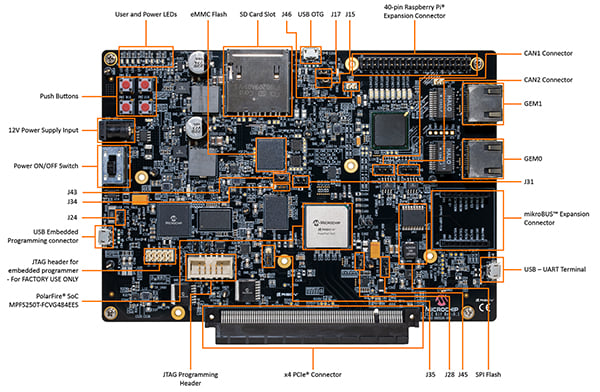

Aby przyspieszyć projektowanie systemów z wykorzystaniem układu SoC bezpośrednio programowalnej macierzy bramek (FPGA) PolarFire, firma Microchip oferuje zestaw MPFS-ICICLE-KIT-ES PolarFire SoC Icicle, który umożliwia analizę działania pięciordzeniowego podsystemu mikroprocesorowego RISC-V z obsługą systemu Linux i możliwością wykonywania operacji w czasie rzeczywistym przy niskiej mocy. Zestaw zawiera bezpłatną licencję Libero Silver, która jest potrzebna do ewaluacji projektów. Obsługuje ona funkcje programowania i debugowania w jednym języku.

Pracę z układami SoC bezpośrednio programowalnych macierzy bramek (FPGA) wspomaga akceleratorowy zestaw rozwojowy oprogramowania (SDK) VectorBlox, który pozwala na opracowywanie kompaktowych rozwiązań niskiej mocy ze sztuczną inteligencją i uczeniem maszynowym (AI/ML). Nacisk kładziony jest na uproszczenie procesu projektowania do tego stopnia, że projektanci nie muszą mieć wcześniejszego doświadczenia w projektowaniu bezpośrednio programowalnych macierzy bramek (FPGA). Akceleracyjny zestaw rozwojowy oprogramowania (SDK) VectorBlox umożliwia deweloperom programowanie energooszczędnych sieci neuronowych przy użyciu języka C/C++. Zestaw Icicle posiada wiele funkcji tworzących kompleksowe środowisko programistyczne, w tym system czujników z zasilaniem wieloszynowym do monitorowania różnych stref zasilania, główny port PCIe, różne pamięci wbudowane - w tym LPDDR4, QSPI i eMMC Flash - do obsługi systemów Linux i Raspberry Pi oraz porty rozszerzeń mikroBUS na potrzeby wielu opcji łączności przewodowej i bezprzewodowej oraz rozszerzenia funkcjonalne, takie jak funkcja lokalizacji wykorzystująca globalny system nawigacji satelitarnej (GNSS) (ilustracja 5).

Ilustracja 5: W przedstawianym kompleksowym środowisku rozwojowym do układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) znajdują się złącza do płytek rozszerzeń Raspberry Pi (u góry po prawej) i mikroBUS (u dołu po prawej stronie). (Źródło ilustracji: Microchip Technology)

Płytki rozszerzeń

Kilka przykładów płytek rozszerzeń mikroBUS:

MIKROE-986 -zapewnienie dodatkowej łączności przez magistralę CAN z wykorzystaniem szeregowego interfejsu urządzeń peryferyjnych (SPI).

MIKROE-1582 - interfejs pomiędzy mikrokontrolerem MCU i magistralą RS-232.

MIKROE-989 - łączenie z magistralą komunikacyjną RS422/485.

MIKROE-3144 - obsługa technologii LTE kat. M1 i NB1 umożliwiająca niezawodną i prostą łączność z urządzeniami Internetu rzeczy (IoT) 3GPP.

MIKROE-2670 - dodanie funkcji lokalizacji z wykorzystaniem globalnego systemu nawigacji satelitarnej (GNSS) z równoczesnym odbiorem konstelacji systemów GPS i Galileo oraz BeiDou lub GLONASS, zapewniające wysoką dokładność pozycji w przypadku słabego sygnału lub zakłóceń w miejskich kanionach.

Podsumowanie

Podczas opracowywania połączonych, krytycznych dla bezpieczeństwa deterministycznych systemów ścisłego czasu rzeczywistego, projektanci mogą sięgnąć po układy SoC bezpośrednio programowalnych macierzy bramek (FPGA). Układy SoC bezpośrednio programowalnych macierzy bramek (FPGA) zapewniają szeroką gamę elementów systemowych, w tym sieć szkieletową FPGA, podsystem mikrokontrolera MCU RISC-V z pamięciami o wysokich parametrach działania, szybkie interfejsy komunikacyjne i liczne funkcje zabezpieczeń. W rozpoczęciu pracy projektantom mogą pomóc dostępne płytki i środowiska rozwojowe zawierające wszystkie niezbędne elementy, w tym płytki rozszerzeń, których można używać do wdrażania szerokiego zakresu funkcji komunikacyjnych i lokalizacyjnych.

Rekomendowane artykuły

- Wdrażanie technologii sieci wrażliwych na czas w celu zapewnienia komunikacji deterministycznej

- Systemy operacyjne czasu rzeczywistego (RTOS) i ich zastosowania

Autor: Jeff Shepard

Kontakt w Polsce: Arkadiusz Rataj

Sales Manager Central Eastern Europe & Turkey

Digi-Key Electronics Germany

0048 696 307 330

arkadiusz.rataj@digikey.com

poland.support@digikey.pl

Zapraszamy na jednodniowe targi elektroniki we Wrocławiu! Zapisz się