Użycie układów FPGA w projektowaniu systemów czasu rzeczywistego

Aby sprostać wyzwaniom projektowym można wykorzystać układy SoC bezpośrednio programowalnych macierzy bramek (FPGA), tworząc inteligentne, spójne i deterministyczne systemy.

Większa moc obliczeniowa przy mniejszym zużyciu energii

Poza korzyściami związanymi z działaniem systemu, takim jak obsługa przetwarzania ścisłego czasu rzeczywistego, omawiane układy SoC bezpośrednio programowalnych macierzy bramek (FPGA) charakteryzują się wysoką sprawnością energetyczną. Test porównawczy EEMBC CoreMark-PRO jest standardem branżowym porównującym sprawność i parametry działania mikrokontrolerów MCU w systemach wbudowanych. Został zaprojektowany specjalnie do testów porównawczych działania sprzętu i zastąpił test porównawczy Dhrystone.

Testy obciążeniowe CoreMark-PRO obejmują różnorodne charakterystyki parametrów działania, równoległość na poziomie instrukcji i wykorzystanie pamięci w oparciu o cztery obciążenia zmiennoprzecinkowe i pięć typowych obciążeń całkowitoliczbowych. Obciążenia zmiennoprzecinkowe obejmują liniową procedurę algebraiczną pochodzącą z biblioteki LINPACK, szybką transformację Fouriera, algorytm sieci neuronowej do ewaluacji wzorca oraz ulepszoną wersję testu pętli Livermore. Podstawę obciążeń całkowitoliczbowych stanowią kompresja JPEG, analizator XML, kompresja ZIP i 256-bitowy bezpieczny algorytm skrótu (SHA-256).

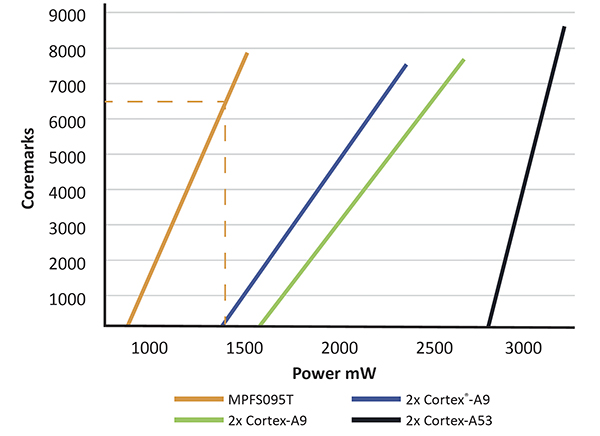

Modele MPFSO95T omawianych układów SoC bezpośrednio programowalnej macierzy bramek (FPGA), takich jak MPFS095TL-FCSG536E, są w stanie osiągnąć 6500 punktów CoreMark przy mocy 1,3W (ilustracja 3).

Ilustracja 3: Układ SoC bezpośrednio programowalnej macierzy bramek (FPGA) MPFS095T (pomarańczowa linia) uzyskuje 6500 punktów Coremark przy mocy 1,3W. (Źródło ilustracji: Microchip Technology)

Kwestie dotyczące zabezpieczeń

Zastosowania kluczowe dla bezpieczeństwa i ścisłego czasu rzeczywistego omawianych układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) oprócz wysokiej sprawności energetycznej i zaawansowanych możliwości przetwarzania wymagają silnych zabezpieczeń. Podstawowe funkcje zabezpieczeń omawianych układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) to m.in. programowanie strumienia bitowego odporne na różnicową analizę mocy (DPA), generator liczb prawdziwie losowych (TRNG) i funkcja uniemożliwiająca fizycznie klonowanie (PUF). Obejmują one również standardowe i zdefiniowane przez użytkownika bezpieczne uruchamianie, ochronę pamięci fizycznej, która zapewnia ograniczenia dostępu do pamięci w zależności od stanu uprawnień komputera, w tym trybu maszyny, nadzorcy lub użytkownika, oraz odporność na ataki typu Meltdown i Spectre.

Zabezpieczenia zaczynają się od bezpiecznego zarządzania łańcuchem dostaw, w tym stosowania modułów zabezpieczeń sprzętowych (HSM) podczas testowania płytek i pakowania. Zastosowanie 768-bajtowego, podpisanego cyfrowo certyfikatu bezpośrednio programowalnej macierzy bramek (FPGA) X.509 osadzonego w każdym układzie SoC FPGA zwiększa niezawodność łańcucha dostaw.

W układach SoC bezpośrednio programowalnych macierzy bramek (FPGA) znajduje się wiele wbudowanych urządzeń do wykrywania nieautoryzowanych ingerencji, które zapewniają bezpieczne i niezawodne działanie. W przypadku wykrycia próby nieautoryzowanej ingerencji system może odpowiednio zareagować. Niektóre z dostępnych urządzeń do wykrywania nieautoryzowanej ingerencji:

- Monitory napięcia

- Czujniki temperatury

- Detektory zakłóceń zegara i częstotliwości zegara

- Aktywny detektor JTAG

- Aktywny detektor sieci kratowej

Bezpieczeństwo jest dodatkowo zapewnione dzięki środkom zapobiegającym atakom z wykorzystaniem korelacyjnej analizy mocy (CPA), wyposażonym w 256-bitowy symetryczny szyfr blokowy w zaawansowanym standardzie szyfrowania AES-256, zintegrowanym funkcjom skrótu kryptograficznego zapewniającym integralność danych, zintegrowanej funkcji uniemożliwiającej fizycznie klonowanie do przechowywania kluczy oraz możliwości wyzerowania sieci szkieletowej bezpośrednio programowalnej macierzy bramek (FPGA) i wszystkich pamięci w układzie.