Czy należy kierować sygnały w płaszczyźnie zasilania PCB?

Istnieje wiele aspektów, które należy wziąć pod uwagę podczas trasowania sygnałów w warstwie zasilania lub podczas trasowania szyn zasilania w warstwie sygnału.

Często otrzymuję pytania od projektantów dotyczące takich kwestii jak integralność sygnału i integralność zasilania, a ostatnie pytanie zmusiło mnie do przemyślenia (ponownie!) niektórych podstawowych praktyk dotyczących wyznaczania tras ścieżek w pobliżu płaszczyzn i elementów miedzianych. Oto (sparafrazowane) pytanie, które niedawno otrzymałem w serwisie LinkedIn:

Interesuje mnie Pana pogląd na łączenie sygnału/zasilania na tej samej warstwie w układzie PCB. Czy można poprowadzić ścieżki sygnałowe na tej samej warstwie co płaszczyzny zasilania? Znane mi są zasady dotyczące budowania stosu, z których wynika, że można tak robić, ale nikt nie podaje solidnych wskazówek.

Po raz kolejny mamy świetny przykład stosowanych od dawna wytycznych dotyczących projektowania podawanych bez wystarczającego kontekstu. Krótka odpowiedź na to pytanie brzmi „tak, w pewnych sytuacjach można tak robić”. Praktyka ta jest dość powszechna i stosujemy ją na płytkach klientów bez żadnych problemów z impedancją, kompatybilnością elektromagnetyczną lub utratą zasilania prądem stałym w tych produktach, ponieważ stos został zaprojektowany poprawnie i pomyśleliśmy o tym, jak odpowiednio poprowadzić ścieżki w projekcie. Istnieje jednak wiele aspektów, które należy wziąć pod uwagę podczas trasowania sygnałów w warstwie zasilania lub podczas trasowania szyn zasilania w warstwie sygnału. Trudności wynikają z rozważań dotyczących integralności zasilania, kontrolowanej impedancji i dystrybucji zasilania prądem stałym na płytce.

Jak kierować sygnały w warstwie płaszczyzny zasilania PCB

Zanim zaczniemy rozcinać warstwę płaszczyzny zasilania PCB za pomocą ścieżek, należy przemyśleć wymagania projektowe w następujących obszarach:

- Obciążalność prądowa płaszczyzny mocy

- Sygnały i impedancja o niskiej i dużej prędkości

- Ścieżki powrotne, jeśli płaszczyzna jest używana jako warstwa odniesienia

Przyjrzyjmy się teraz każdemu z tych obszarów bardziej szczegółowo.

Obciążalność prądowa płaszczyzny zasilania

Za każdym razem, gdy projektujemy płaszczyznę zasilania, będzie ona miała określoną obciążalność prądową, która jest związana z grubością miedzi tworzącej warstwę płaszczyzny. Jeśli zaczniemy prowadzić ścieżki przez płaszczyznę o dużej mocy, płaszczyzna zostanie podzielona na sekcje, a każda sekcja będzie mieć niższą wydajność prądową niż jednolita warstwa płaszczyzny. Ponadto, jeśli kształt warstwy mocy jest bardzo złożony, może powstać miejsce o dużej gęstości prądu, które może się dość mocno nagrzewać. Warto wizualizować takie efekty w symulacji analizatora PDN (zobacz przykład w tym artykule).

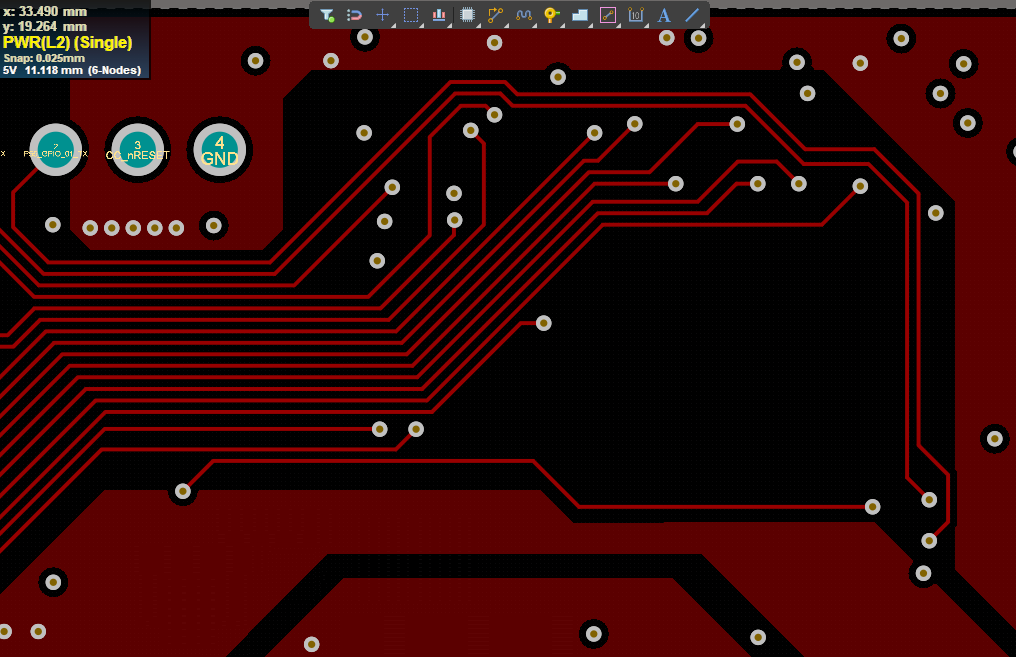

Ten obszar w wysokoprądowej płaszczyźnie zasilania może działać jak punkt dławiący o niższej wydajności prądowej.

Ten obszar w wysokoprądowej płaszczyźnie zasilania może działać jak punkt dławiący o niższej wydajności prądowej.

Jednym ze sposobów na rozwiązanie problemów z prowadzeniem ścieżek na płaszczyźnie mocy jest użycie innej płaszczyzny mocy na sąsiedniej warstwie, która przebiega równolegle. W tym układzie prąd zostanie w rzeczywistości rozdzielony na dwie równoległe płaszczyzny, co pomoże zagwarantować, że wartość obciążalności prądowej w żadnej sekcji płaszczyzny nie zostanie przekroczona. W przypadku większości urządzeń o niskim poborze mocy na ogół nie trzeba się o to martwić. Jeśli jednak mamy do czynienia z systemem o dużej mocy, prawdopodobnie trzeba będzie podjąć takie działania, aby system mógł zapewnić wystarczającą moc bez nadmiernego nagrzewania się. Jednym z typowych przykładów, w których jest to stosowane, są płyty montażowe (3U/6U) lub inne jednostki montowane na stelażu.

Impedancja ścieżki

Jeśli ścieżki o kontrolowanej impedancji nie są prowadzone przez warstwę miedzianą na płaszczyźnie mocy, nie trzeba nadmiernie rozważać tego problemu. Protokoły cyfrowe single-ended, takie jak SPI i I2C, a także GPIO, mogą być prowadzone przez miedziane warstwy bez obawy o impedancję, ponieważ nie mają specyfikacji impedancji, ale nadal należy postępować zgodnie z innymi wytycznymi z tej listy (w stosownych przypadkach). Protokoły wysokiej prędkości, w których ważna jest impedancja, to inna kwestia wymuszająca zapewnienie wystarczającej ilości miedzi na odstępy wokół tych ścieżek, aby cele impedancji nie zostały naruszone. Jeśli płytka zasilająca znajduje się zbyt blisko ścieżek, trzeba przeprowadzić obliczenia współpłaszczyznowe w stosie warstw, aby upewnić się, że nie zostanie naruszona tolerancja impedancji.

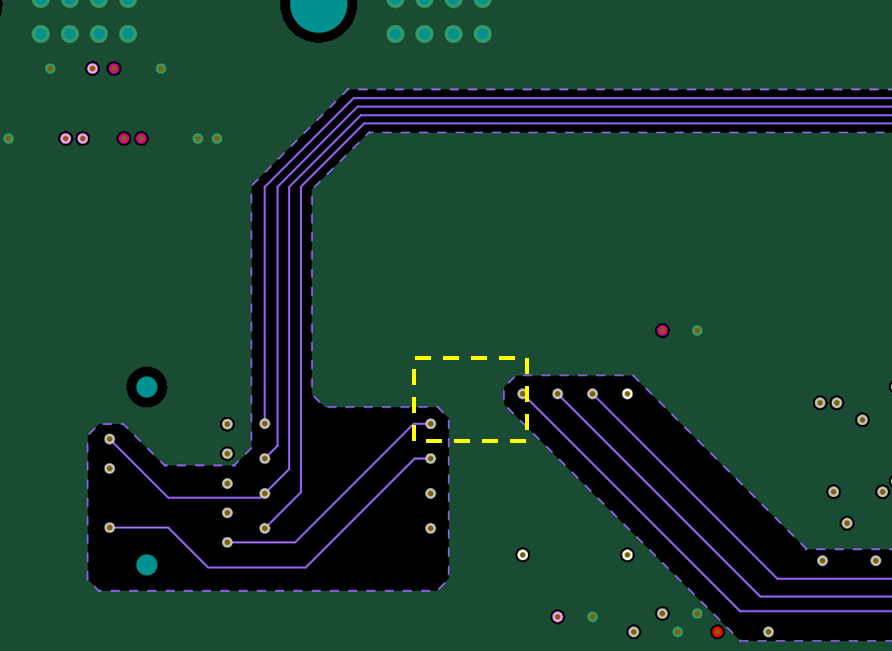

W tym przykładzie wyczyściłem płaszczyznę zasilania, ponieważ ułatwia to trasowanie ścieżek w tej warstwie. Warto zwrócić uwagę, że pominąłem również miedź z dużego centralnego obszaru, ponieważ nie zapewnia ona żadnej użytecznej funkcji ze względu na zasady dotyczące odstępów na tej płytce.

W tym przykładzie wyczyściłem płaszczyznę zasilania, ponieważ ułatwia to trasowanie ścieżek w tej warstwie. Warto zwrócić uwagę, że pominąłem również miedź z dużego centralnego obszaru, ponieważ nie zapewnia ona żadnej użytecznej funkcji ze względu na zasady dotyczące odstępów na tej płytce.

Niebezpieczeństwo związane z rozcięciem płaszczyzny spowodowanym zastosowaniem dużych odstępów polega na tym, że warstwa miedzi zostanie rozcięta na zbyt wiele sekcji. Jeśli zostanie poprowadzonych zbyt wiele ścieżek, pozostanie wiele resztek miedzi wokół układu, które zostaną pocięte na małe sekcje. W przypadku płytki o małej liczbie warstw, która wymaga również kontroli impedancji, może nie być oddzielnej warstwy zasilania, której można użyć do połączenia wszystkich tych sekcji. Jeśli okaże się, że trzeba poprowadzić dużą liczbę ścieżek przez warstwę zasilania, lepszym rozwiązaniem może być dodanie dwóch dodatkowych warstw (zasilania i uziemienia).

Ścieżki powrotne i wyznaczanie tras ścieżek przez podziały płaszczyzny zasilania

Podobnie jak przy prowadzeniu wszelkich innych ścieżek, należy się upewnić, że ścieżka powrotna dla sygnałów na PCB jest dobrze zdefiniowana. Jest to szczególnie ważne w przypadku prowadzenia ścieżek w warstwie zasilania. Problem pojawia się, jeśli ścieżka zostaje wyznaczona na sąsiedniej warstwie. Prowadzenie ścieżki na tej samej warstwie co płaszczyzna zasilania powoduje powstanie przerw w płaszczyźnie odniesienia. W przypadku płaszczyzn mocy jest to generalnie poprawne rozwiązanie, o ile płaszczyzna mocy nie jest używana jako odniesienie dla sygnałów na innej warstwie. Jeśli w konsekwencji zdarzy się, że ścieżka zostanie poprowadzona przez jedną z tych przerw, powstanie obszar o wyższej indukcyjności pasożytniczej, który może następnie odbierać więcej zakłóceń EMI z przesłuchów lub źródeł zewnętrznych.

W przypadku protokołów o niższej prędkości rozchodzących się między dwiema warstwami płaszczyzny prawdopodobnie można sobie pozwolić na ścieżkę po podzielonej płaszczyźnie mocy, o ile płaszczyzna w drugiej warstwie jest jednolita. Nieciągłość impedancji, która zostanie utworzona, będzie elektrycznie krótka, więc nie trzeba się martwić o odbicia, a obecność płaszczyzny na drugiej warstwie pomaga zagwarantować, że nadal istnieje dobrze zdefiniowana ścieżka powrotna, pomimo wyższej indukcyjności w obszarze z podzieloną płaszczyzną. W przypadku sygnałów o wyższej prędkości jest to znacznie ważniejsze i prawdopodobnie lepiej będzie dodać nową warstwę, aby zrobić miejsce na te sygnały, niż rozdzielać płaszczyznę zasilania.

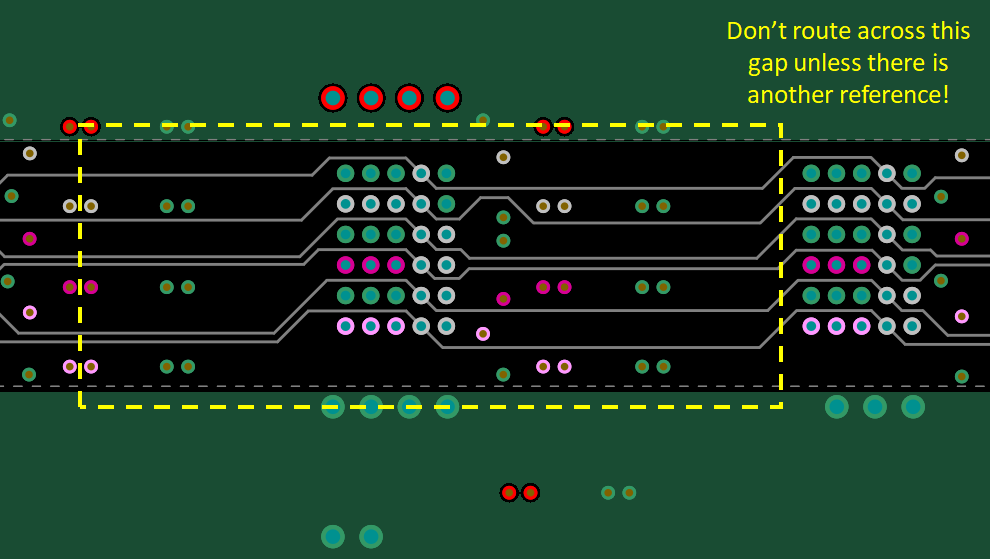

W przypadku protokołów o wyższej prędkości pojawia się problem z trasowaniem linii paskowej przez tego rodzaju podział w warstwie płaskiej, na co zwrócili uwagę inni autorzy. Załóżmy na przykład, że poprowadzimy linię paskową między warstwą zasilania a warstwą uziemienia, a warstwa uziemienia jest podzielona z powodu prowadzenia ścieżek na warstwie zasilania. Będzie to wyglądać jak w poniższym modelu.

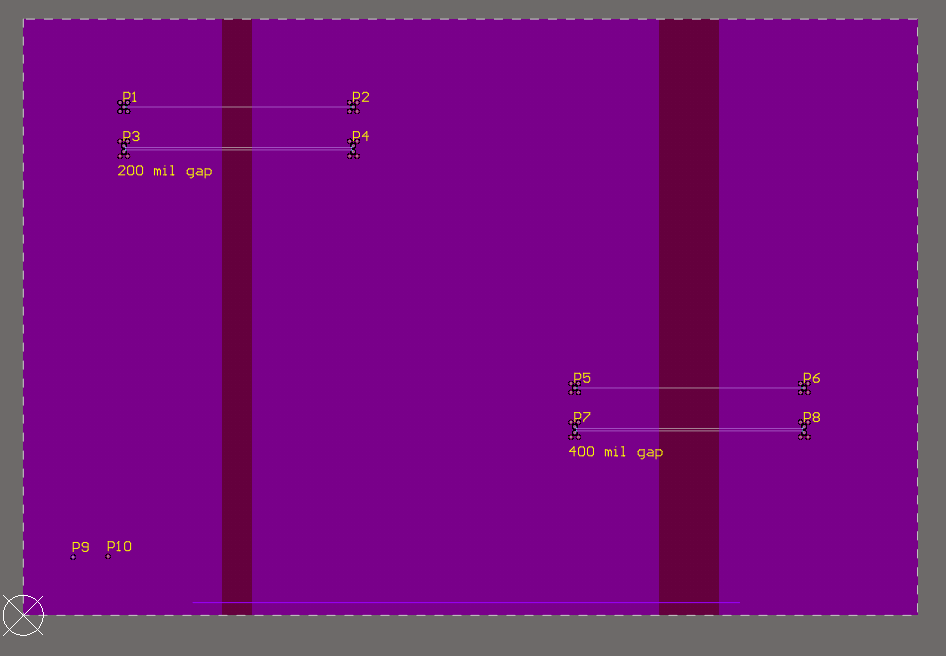

Tutaj przedstawiam bardzo podstawowy model, który może zostać wykorzystany w symulacji integralności sygnału. Sygnały zaczynają się od pól lutowniczych uziemienia na górnej warstwie (L1), a w warstwie płaszczyzny zasilania (L2) znajdują się dwa podziały, które można wykorzystać do trasowania sygnałów. Na kolejnej sąsiedniej warstwie sygnału (L3) mamy dwie grupy linii paskowych o zdefiniowanej impedancji (single-ended 50 omów, para różnicowa 100 omów). Sygnały te są kierowane przez płaszczyznę uziemienia na warstwę L4. Wszystkie dielektryki mają grubość 10 mil przy Dk = 4/Df = 0,02. Przelotki sygnałowe mają dodane przelotki zszywające, aby zapewnić dopasowaną impedancję wejściową do linii paskowych w każdej konfiguracji.

Z tego modelu symulacyjnego wynika, że ścieżki są prowadzone przez podziały w warstwie zasilania. Jeden podział (lewa strona) jest wąski (200 mil), a drugi (prawa strona) jest szerszy (400 mil). Jak wpłynie to na impedancję i odbicia, biorąc pod uwagę, że na warstwie L4 znajduje się płaszczyzna uziemienia?

Po pierwsze, w każdym obszarze przerwy występuje niezgodność impedancji. Kanał single-ended ma impedancję charakterystyczną 58,1 oma w obszarze przerwy, podczas gdy kanał różnicowy ma 106,2 oma charakterystycznej impedancji różnicowej. Różnica ta nie powinna być zaskakująca, ponieważ kanały różnicowe mają impedancję zdefiniowaną przez odstęp między dwiema ścieżkami w parze.

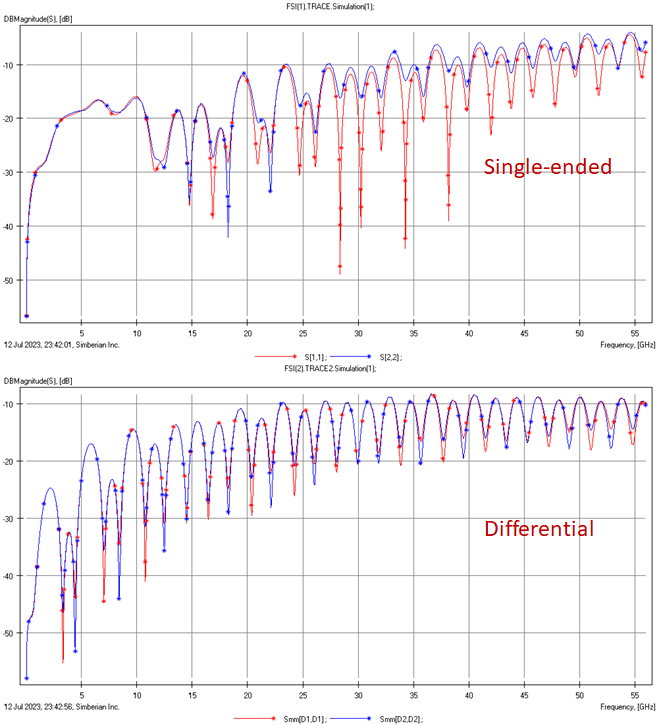

Chociaż istnieje wyraźne niedopasowanie, kolejnym pytaniem jest, czy ma to znaczenie w każdym kanale. Aby to ustalić, możemy spojrzeć na parametry S i impedancję w obszarze przerwy. Oczekiwalibyśmy, że przy niskich częstotliwościach szczelina będzie niewidoczna i nie będzie mieć większego wpływu na impedancję. Jednak przy wyższych częstotliwościach spodziewalibyśmy się, że szczelina spowoduje zauważalną zmianę w stratach powrotnych. Poniższe wykresy przedstawiają wyniki symulacji Simbeor ilustrujące straty powrotne (S11) w przypadku kanałów poprowadzonych przez szczelinę o szerokości 200 mil.

Podczas trasowania przez szczelinę o szerokości 200 mil wyniki nie są tak straszne. Chociaż zazwyczaj widzimy straty powrotne na poziomie -30 dB lub niższym, często jesteśmy skłonni zaakceptować wszystko poniżej –10 dB, gdy przechodzimy do wyższych częstotliwości. Zarówno kanały single-ended, jak i różnicowe spełniają te kryteria do około 20–25 GHz.

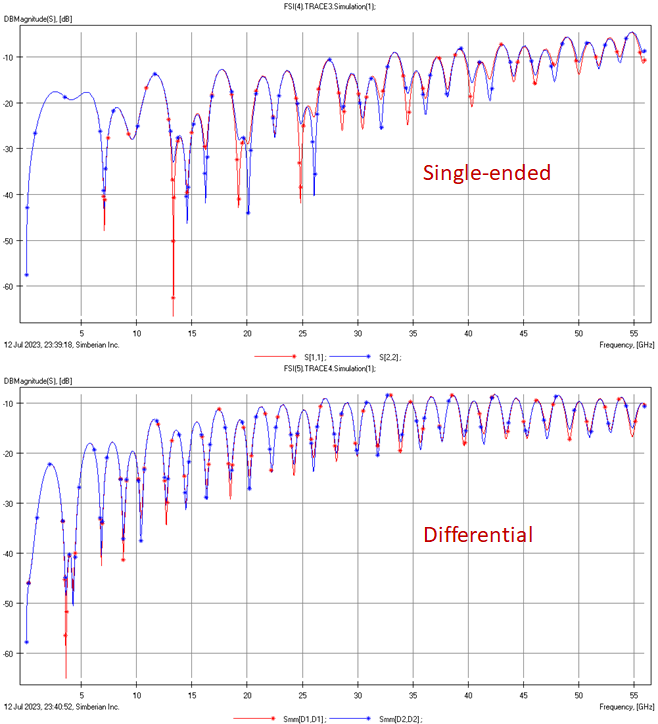

Teraz możemy porównać te wyniki z przypadkiem poprowadzenia ścieżki przez szczelinę o szerokości 400 mil – jak pokazano poniżej.

Nawet poprzednie wyniki są niepożądane, a te, zgodnie z oczekiwaniami, są nieco gorsze. Nadal widzimy, że spektrum strat powrotnych zbliża się do akceptowalnego limitu zarówno dla kanałów różnicowych, jak i single-ended poprowadzonych przez szczelinę o szerokości 400 mil. W tych kanałach możemy oszacować, że szczelina spowoduje dodanie około 20–25 dB strat powrotnych, w zależności od częstotliwości, przy założeniu, że zaczynamy od bazowej wartości S11 wynoszącej -35–40 dB.

Co się stanie, jeśli poprowadzimy ścieżki w tych szczelinach w warstwie zasilania? Wydawać by się mogło, że wystąpią pewne przesłuchy ze ścieżek w powyższej warstwie. Tymczasem obecność płaszczyzny zasilania i płaszczyzny uziemienia wspólnie określa impedancję. Wystąpiłyby jednocześnie przesłuchy i odbicia, a wartość każdego z nich byłaby bardziej widoczna przy wyższych szerokościach pasma. Potwierdza to powyższe punkty dotyczące czasu narastania – linie paskowe przenoszące wolniejsze sygnały mogą być prowadzone przez szczelinę w warstwie zasilania, ale szybsze sygnały będą miały szerokość pasma pokrywającą się ze spadkiem widma strat powrotnych, a kanał może być niefunkcjonalny.

Streszczenie

Podsumowując, nie martwiłbym się zbytnio o prowadzenie ścieżek w miedzianej warstwie, jeśli pracujemy z sygnałami cyfrowymi o niższej prędkości, które nie wymagają kontroli impedancji. Wystarczy pamiętać o ścieżce prądu elektrycznego przy płaszczyźnie zasilania i starać się nie ciąć warstwy mocy na małe wyspy. W innych przypadkach należy użyć dodatkowej warstwy i to na niej prowadzić trasy ścieżek. Ponadto należy pamiętać o wymaganiach dotyczących impedancji: miedź współpłaszczyznowa w warstwie zasilania, która jest umieszczona zbyt blisko linii paskowych lub mikropasków, spowoduje odchylenie impedancji, podobnie jak w przykładzie, który pokazuję przy użyciu mikropasków współpłaszczyznowych.

A co zrobić z sygnałami sąsiadującymi z płaszczyzną zasilania? W przypadku sygnałów o umiarkowanej prędkości należy się upewnić, że w pobliżu znajduje się inna płaszczyzna odniesienia, i unikać prowadzenia ścieżek przez szczeliny w warstwie zasilania. W przypadku bardzo szybkich sygnałów łatwo można zauważyć, że nawet przy sąsiedniej płaszczyźnie uziemienia (konfiguracja linii paskowej) nadal będzie występować nieciągłość impedancji. Jeśli szczelina w warstwie zasilania jest większa, niedopasowanie impedancji będzie widoczne przy niższych częstotliwościach i spowoduje więcej odbić.

O autorze

Zachariah Peterson ma bogate doświadczenie techniczne w środowisku akademickim i przemysłowym. Obecnie prowadzi badania, projekty oraz usługi marketingowe dla firm z branży elektronicznej. Przed rozpoczęciem pracy w przemyśle PCB wykładał na Portland State University i prowadził badania nad teorią laserów losowych, materiałami i stabilnością. Jego doświadczenie w badaniach naukowych obejmuje tematy związane z laserami nanocząsteczkowymi, elektroniczne i optoelektroniczne urządzenia półprzewodnikowe, czujniki środowiskowe i stochastykę. Jego prace zostały opublikowane w kilkunastu recenzowanych czasopismach i materiałach konferencyjnych. Napisał ponad 2000 artykułów technicznych na temat projektowania PCB dla wielu firm. Jest członkiem IEEE Photonics Society, IEEE Electronics Packaging Society, American Physical Society oraz Printed Circuit Engineering Association (PCEA). Wcześniej był członkiem z prawem głosu w Technicznym Komitecie Doradczym INCITS Quantum Computing pracującym nad technicznymi standardami elektroniki kwantowej, a obecnie jest członkiem grupy roboczej IEEE P3186 zajmującej się interfejsem reprezentującym sygnały fotoniczne przy użyciu symulatorów obwodów klasy SPICE.

Artykuł opublikowano dzięki uprzejmości firmy Altium

Kontakt w Polsce: Paweł Czyż 692 273 540