Kompaktowe i wysokosprawne zasilanie dla układów FPGA

Zasilanie macierzy FPGA to złożona funkcja o znaczeniu krytycznym, zawierająca dużą liczbę i różnorodność szyn zasilających, z których część wymaga dostarczania nawet 50A w krótkim czasie.

Bezpośrednio programowalne macierze bramek (FPGA) są coraz częściej wykorzystywane w wysokowydajnych obliczeniach w procesach przetwarzania obrazu i wideo, systemach medycznych, motoryzacji, lotnictwie oraz sztucznej inteligencji i uczeniu maszynowym. Zasilanie macierzy FPGA to złożona funkcja o znaczeniu krytycznym, zawierająca dużą liczbę i różnorodność szyn zasilających, z których część wymaga dostarczania nawet 50A w krótkim czasie.

Prawidłowe działanie macierzy FPGA wymaga sekwencjonowania włączania i wyłączania szyn zasilających, monotonicznego narastania i opadania, a także wysokiej dokładności napięcia i szybkich odpowiedzi impulsowych. Ponadto regulatory prądu stałego dostarczające napięcia o różnych wartościach muszą mieć niewielkie rozmiary, umożliwiające umieszczenie w pobliżu macierzy FPGA w celu minimalizacji zjawisk pasożytniczych w liniach rozdziału zasilania, a także charakteryzować się wysoką sprawnością w celu minimalizacji wzrostu temperatur w pobliżu macierzy FPGA. W pewnych układach regulatory prądu stałego muszą być na tyle cienkie, aby można je było zamontować z tyłu płytki drukowanej.

Zaprojektowanie regulatorów prądu stałego o wysokiej sprawności i parametrach działania z niezbędnym zintegrowanym cyfrowym zarządzaniem zasilaniem jest możliwe, jednak uzyskanie bardzo kompaktowego, płaskiego formatu jest nie lada wyzwaniem. Trudność ta może skutkować licznymi iteracjami projektu i odciągać uwagę od projektowania układu macierzy FPGA, opóźniając wprowadzenie produktu na rynek i obniżając parametry działania układu.

Projektanci układów zasilania FPGA mogą wykorzystać w pełni przetestowane i zweryfikowane zintegrowane regulatory prądu stałego zawierające wszystkie komponenty, zamknięte w termicznie wydajnych obudowach typu LGA (Land Grid Array) i BGA (Ball Grid Array), nadających się do integracji bezpośrednio przy macierzach FPGA w celu maksymalizacji parametrów działania układu zasilania (i macierzy FPGA).

W artykule omówiono wymagania macierzy FPGA w dziedzinie zasilania ze szczególnym uwzględnieniem dokładności napięć, odpowiedzi impulsowych i sekwencjonowania napięć, a także wyzwania związane z odprowadzaniem ciepła na przykładach użytkowych. Następnie przedstawiono zintegrowane regulatory prądu stałego firmy Analog Devices przeznaczone do zasilania macierzy FPGA, w tym regulatory niskoprofilowe, które można zamontować z tyłu płyty drukowanej, oraz płytki ewaluacyjne i sugestie dotyczące integracji w celu przyspieszenia procesu projektowania.

Wymagania dotyczące zasilania macierzy FPGA

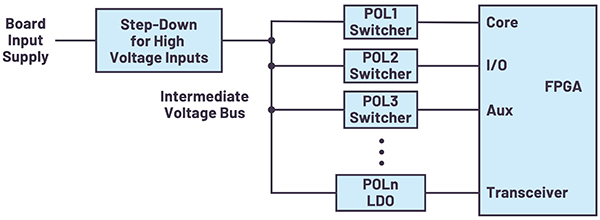

Funkcje w macierzach FPGA, np. rdzeń logiczny, obwody wejścia-wyjścia, obwody pomocnicze i nadajniko-odbiorniki, wymagają stosowania różnych szyn zasilających. Są one zwykle zasilane za pomocą architektury zasilania rozproszonego zawierającej jeden lub kilka regulatorów prądu stałego, zwanych również regulatorami w punkcie obciążenia (PoL), dla każdej szyny zasilającej. Większość z tych regulatorów wykorzystuje impulsową konwersję mocy w celu maksymalizacji sprawności, jednak wrażliwe na zakłócenia obwody - takie jak nadajniko-odbiorniki - mogą wymagać użycia liniowych regulatorów napięcia o niskim spadku (LDO).

W niewielkich układach wspólne napięcie dystrybucyjne wynosi zwykle 5 lub 12V=, co pozwala na bezpośrednie zasilanie regulatorów w punkcie obciążenia (PoL). W większych układach napięcie dystrybucyjne może wynosić 24 lub 48V=. W przypadku stosowania wyższych napięć dystrybucyjnych wykorzystuje się regulator obniżający, którego zadaniem jest obniżenie napięcia dystrybucyjnego do 5 lub 12V= na magistrali napięcia pośredniego zasilającej regulatory PoL. Regulatory PoL dostarczają niskie napięcia wymagane przez poszczególne szyny zasilające macierze FPGA (ilustracja 1). Każda szyna zasilająca ma określone wymagania m.in. w zakresie dokładności, odpowiedzi impulsowej czy sekwencjonowania.

Ilustracja 1: Do zasilania macierzy FPGA potrzebnych jest wiele regulatorów w punkcie obciążenia (PoL). (Źródło ilustracji: Analog Devices)

Regulator PoL rdzenia jest zwykle najważniejszym źródłem zasilania macierzy FPGA. Napięcie rdzenia może wynosić poniżej 1V=, natężenie prądu może sięgać dziesiątek amperów, a wymagana dokładność to co najmniej ±3%, aby zapobiec błędom logicznym. Na przykład dla macierzy FPGA ze specyfikacją tolerancji napięcia rdzenia ±3%, regulator o dokładności ±1,5% zapewnia kolejne ±1,5% dla stanów nieustalonych. Regulator w punkcie obciążenia (PoL) cechujący się dobrą odpowiedzią impulsową zapewnia solidne parametry działania. Jednak regulator o dokładności ±2% może sprawić, że osiągnięcie wymaganych parametrów będzie trudne. Jedynie ±1% jest dostępne dla odpowiedzi impulsowej, co wymaga dodania kondensatorów obejściowych i może powodować błędy logiczne podczas stanów nieustalonych.

Zalety i wady sekwencjonowania

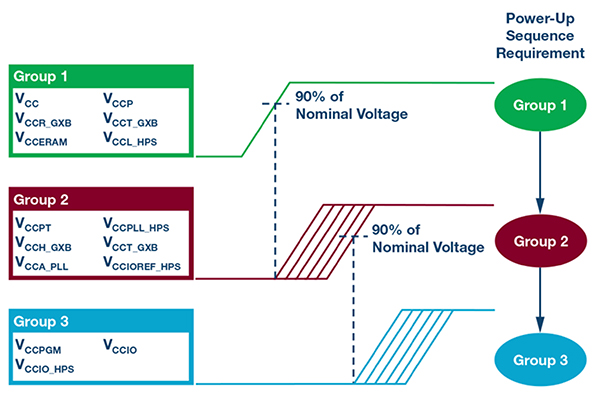

Oprócz wysokich wymagań dotyczących zasilania podczas pracy, macierze FPGA wymagają precyzyjnej synchronizacji włączania i wyłączania różnych szyn zasilających w określonych sekwencjach. Nowoczesne układy FPGA często są wyposażone w liczne szyny zasilające podzielone na kilka grup, które mogą być włączane i wyłączane razem. Na przykład macierze FPGA Altera Arria 10 firmy Intel posiadają strefy zasilania zorganizowane w trzy grupy. Grupy te muszą włączać zasilanie kolejno od grupy 1 (z sześcioma szynami napięciowymi) przez grupę 2 (również sześć szyn napięciowych) do grupy 3 (trzy szyny), a wyłączać w odwrotnej kolejności, aby zapobiec uszkodzeniu macierzy FPGA (ilustracja 2).

Ilustracja 2: Macierze FPGA wymagają włączania i wyłączania szyn zasilających w określonej kolejności. (Źródło ilustracji: Analog Devices)